LPDDR 6 Verification IP

Truechip's LPDDR6 Verification IP provides an effective & efficient way to verify the LPDDR6 components of an IP or SoC. Truechip's LPDDR6 VIP is fully compliant with JESD209-6 LPDDR6 SDRAM standard. The VIP is lightweight, featuring easy-to-use plug-and-play components, so there is no impact on the design cycle time.

Key Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure the highest levels of quality.

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models.

- Exhaustive set of assertions and cover points with connectivity example for all the components.

- Consistency of interface, installation, operation and documentation across all our VIPs.

- Provide a complete solution and easy integration in IP and SoC environment

Features

- Supports LPDDR6 memory densities range up to 64Gb

- Supports two sub-channels contains 12 DQ signals each

- Supports all burst lengths

- Supports capturing of all the valid LPDDR6 commands as per the specification

- Supports per-row activation counting PRAC

- Support for all speed grades

- Constantly monitors LPDDR6 behaviour during simulation

- Supports Programmable READ/WRITE Latency timings

- Supports programming of All-Mode Registers

- Support both Normal and Efficiency Mode Configurations

- Support CS, ZQ Calibration, Command Bus, WCK2CK Levelling, Read DQ Calibration, WCK-DQ, Enhance RDQS and RX Offset Calibration Trainings

- Support all CAS Synchronization operations

- LPDDR6 support 4 banks with 4 bank group per sub-channel

- Supports single-ended clocks, frequency change, and clock stop operations

- Supports refresh, postpone, and pull in of refresh, SRE, PASR, sleep modes, SR power down modes

- Supports Post Package Repair (PPR)

- Supports Link ECC/EDC, On-die ECC, Error Check and Scrub (ECS)

- Supports ZQ, MPC, DCM and DCA, and WCK2CK oscillator

- Supports DVFSC, DVFSQ, ODT, Non-target Dram ODT, thermal sensor, & temperature offset

- Supports RDQS, RDQS toggle mode, and enhanced RDQS mode

- Supports all WCK and RDQS preamble and post-amble patterns

- Supports DBI-DC, Meta Function modes

- Support CA Parity Check modes

- Support Loopback modes

- Reports various timing errors, which can be used to check any timing violations

- It provides full control to the user to enable/disable various types of messages

- Supports advanced System Verilog features like constrained random testing

- Supports dynamically configurable modes

- Strong Protocol Monitor with real-time, exhaustiv,e programmable checks

- Supports RAS Focused – Link Protection

- Supports ALERT output signal

- Supports Dynamic as well as Static Error Injection scenarios

- On the fly protocol checking using protocol check functions, static and dynamic assertion

- Built-in Coverage analysis

- Provides a comprehensive user callbacks in PHY, Controller, and Memory Model BFMs

- Graphical analyser to show transactions for easy debugging

Deliverables

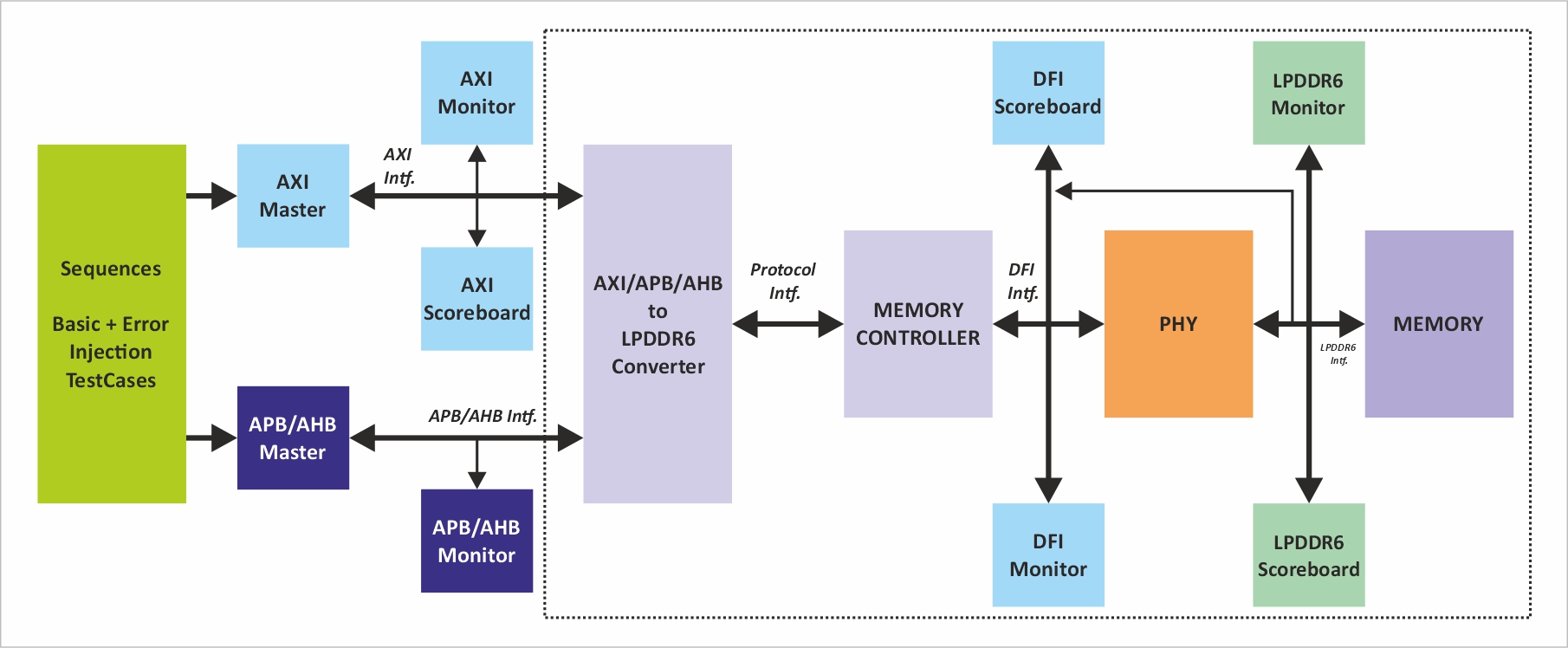

- LPDDR6 Functional memory controller BFM/Agent

- LPDDR6 SDRAM Model

- LPDDR6 Monitor and Scoreboard

- LPDDR6 PHY BFM Model

- LPDDR6 PHY Monitor and Scoreboard

- Test Environment & Test Suite:

- Basic Directed Tests

- Random Tests

- Error Injection Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes